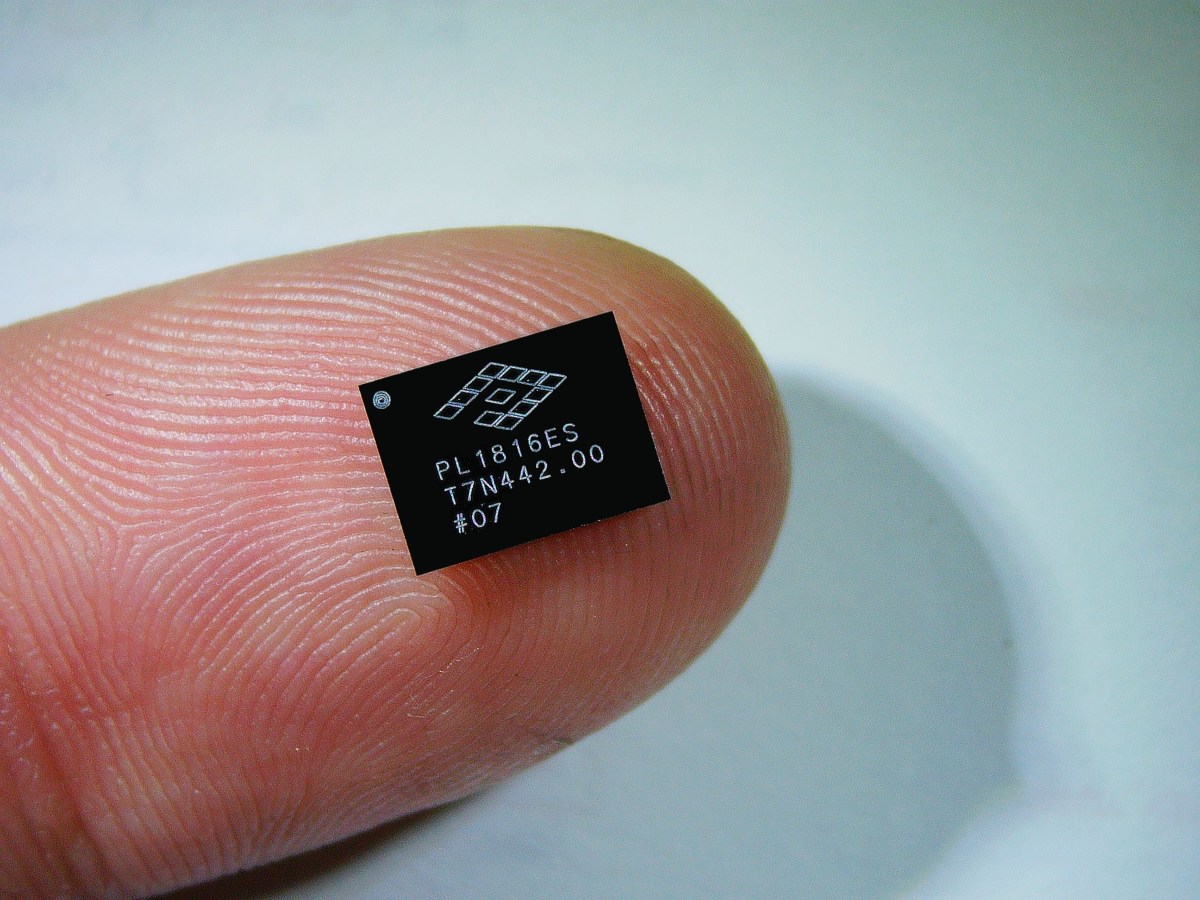

PowerLattice, a startup focused on energy-efficient chip design, secured $25 million in Series A funding led by Pat Gelsinger, former Intel CEO, to advance its power-saving technology. The company claims its chiplet solution reduces energy consumption by over 50%, addressing the growing demand for efficient semiconductor solutions in AI and data centers. Gelsinger praised the team’s expertise, calling their approach a ‘dream team’ for power delivery innovation. PowerLattice’s first chiplets are now being produced by TSMC, with trials planned for 2026 targeting major chipmakers like Nvidia and AMD. The startup faces competition from firms like Empower Semiconductor but aims to capture significant market share through its breakthrough efficiency gains.

Key facts

- PowerLattice raised $25 million in Series A funding, bringing total funding to $31 million.

- The startup’s chiplet technology reduces computer chip power needs by over 50%.

- Pat Gelsinger, former Intel CEO, endorsed PowerLattice’s team as a ‘dream team’ for power delivery innovation.

- PowerLattice’s first chiplets are being produced by TSMC for testing by unnamed manufacturers.

- Potential customers include major chipmakers like Nvidia, AMD, and AI-focused startups such as d-Matrix.